Camera Link High Speed (Camera Link HS or CLHS) is a robust interface standard for industrial cameras and systems. CLHS was introduced in 2012 and built on the low-latency, zero-jitter, real-time strengths of Camera Link. The CLHS standard further provided scalable bandwidths with reliable data delivery, support for both copper and fiber cabling, and, importantly, Intellectual Property (IP) cores for ease of component development. Currently at version 1.1, CLHS implements its protocol with two physical layer encodings: M Protocol and X Protocol. The VHSIC Hardware Description Language (VHDL) IP cores available from A3 have been implemented in Altera, Xilinx, and Microsemi FPGAs. Used in components such as cameras and frame grabbers, the cores are available from A3 at a price point of $1,000 to help promote the standard and speed proliferation of the technology. The inexpensive IP core infrastructure helps camera and frame grabber manufacturers speed CLHS development and implementation. Because CLHS IP core code is open-source, licensed users can customize the core for their own use. They can improve it by adding features that, upon technical review and approval, can become a permanent part of the IP core.

CLHS M/X Protocol IP cores

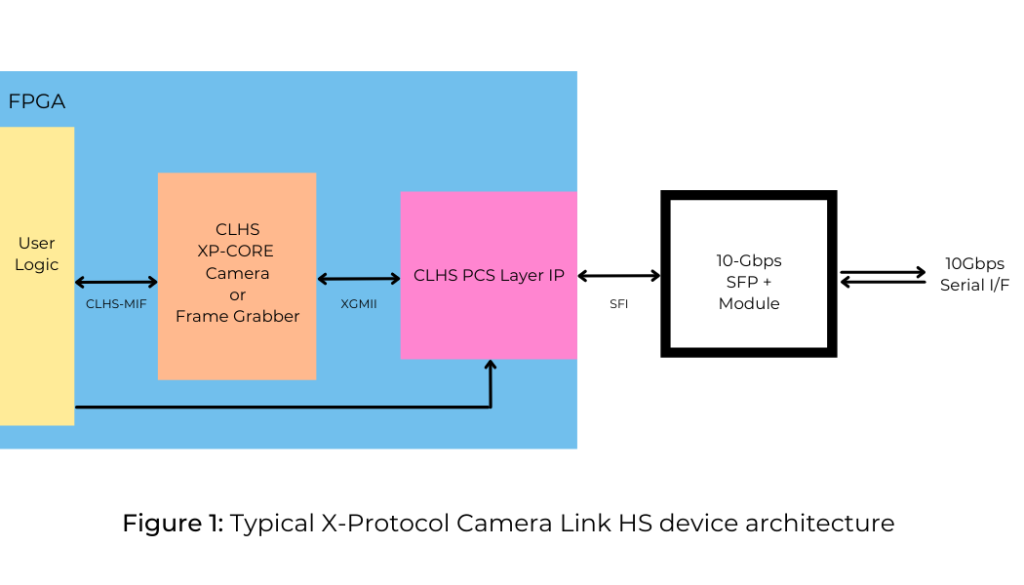

The CLHS M Protocol IP core features 8b/10b line encoding for use in lower-cost and lower-power FPGAs. It supports hardware with copper (C2) cabling, with CX4 connections up to 15m and 2.1Gbps in the CLHS cable. Active plug-on fiber cable can be added externally to achieve up to 100m. Typical bit rates for the M Protocol are up to 5Gbps per lane. The CLHS X Protocol IP core is designed for 10Gbps and higher bit rates using 64b/66b line encoding. Other interface protocols, such as CoaXPress (CXP), are moving to this encoding structure. Note that because of the line encoding technique, CLHS 10Gbps is equivalent to CXP 12.5Gbps. The X Protocol also has forward error correction and single-bit error immunity. This protocol is designed to natively support fiber connections F2 (SFP+) and soon to be introduced F3 – quad small-form-factor pluggable (QSFP+) and multifiber push-on (MPO) – connectors at rates up to 16Gbps per lane. Copper CX4 (C3) connections still are supported, but the highest data rates and cable lengths (as much as 20km or more, in some cases) are realized using fiber cabling. Importantly, the 64b/66b encoded X Protocol has been in production since 2012 and has a long history of field-tested stability.

Five message types are available in CLHS: a low-latency (<1µs) 0ns jitter trigger for real-time imaging at up to 8MHz with seven separate modes, 16 bidirectional general-purpose I/Os with <1µs latency, remote DMA video packet and frame grabber data forwarding, high-speed command uplink enabling streaming correction coefficients, and revision information used in device discovery. One of the big values of CLHS is that it is a real-time, point-to-point interface. In the context of the CLHS triggers and GPIO, the low latency means immediate responses, eliminating the need for tracking and scheduling as might be the case with other interfaces. The CLHS X Protocol can connect to a 10Gbase-KR Ethernet PHY physical (Figure 2) for FPGAs that don't have built in 10Gbps transceivers or use the provided Physical Coding Sublayer (PCS) module to implement the code within 10Gbps-capable FPGAs that don't offer the 10Gbase-KR capability (Figure 3). Because of the unique way the CLHS X Protocol is implemented, Camera Link HS is already in the final stages of moving the specification to 25Gbps.