Easy Interfaces

Reduce Time to Market with Transport Layer IP Cores

Several months of work by protocol engineers is typically required to design an interface for a vision system. A number of vision camera manufactures, such as Ozray, Crevis and Sick, are addressing this challenge by purchasing transport layer interfaces in the form of intellectual property (IP) which is provided ready to incorporate into FPGAs along with other camera features.

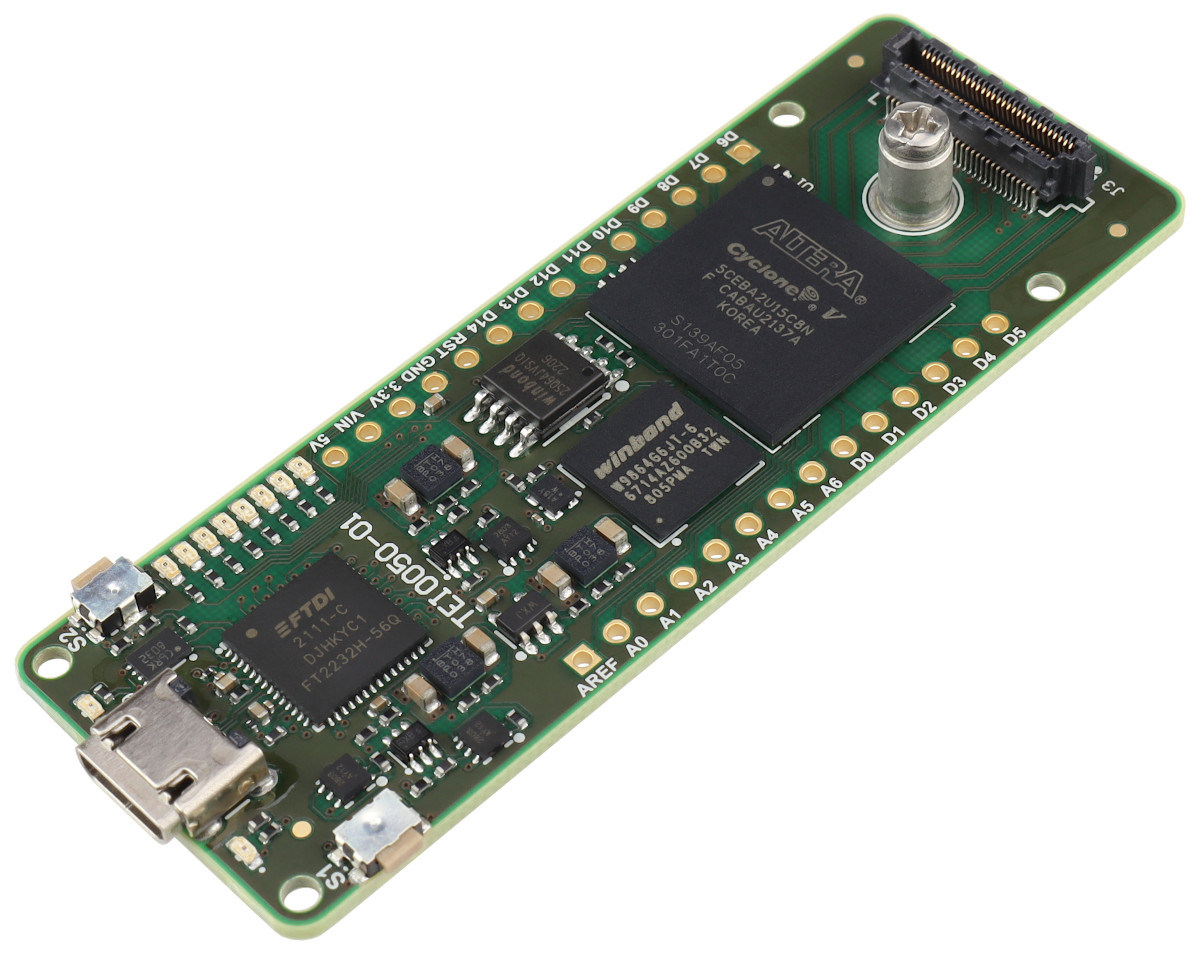

Image 1 | IP cores secure the interoperability of the camera and host while ensuring compliance with the latest version of the interface layer. Sensor to Image´s Vision Standard IP Cores solutions are delivered as a working reference design along with FPGA IP cores. (Image: Euresys s.a.)

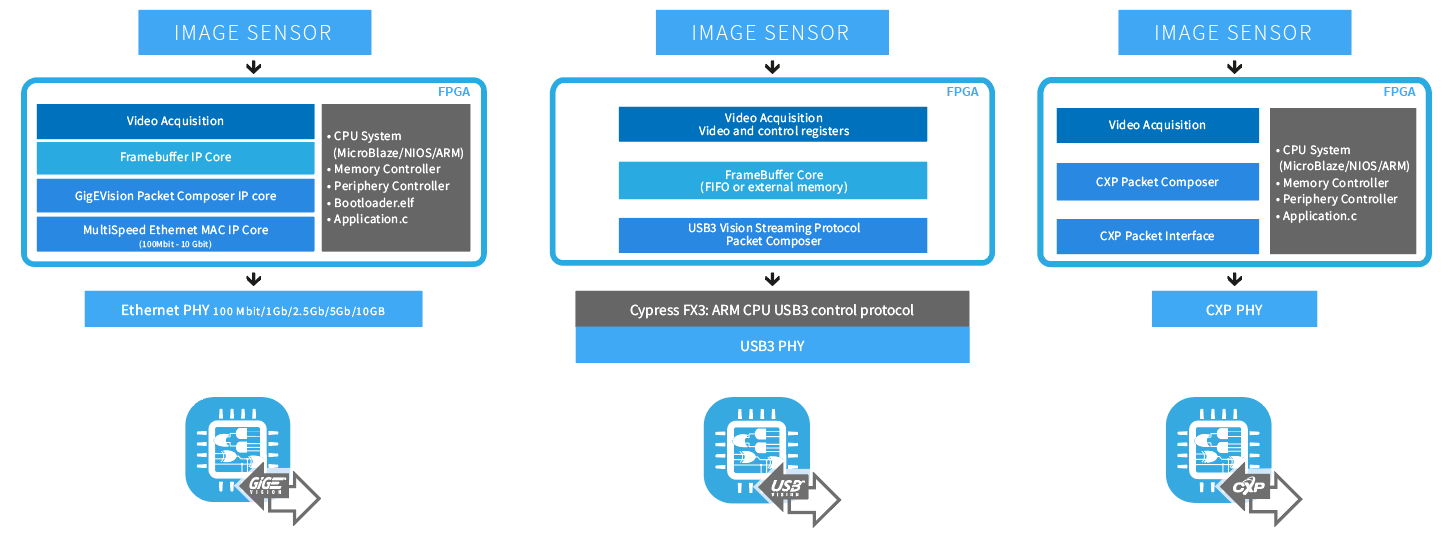

A decade ago, Camera Link was the most widely used machine vision transport layer interface. The streaming part of Camera Link was well defined, but the control path was not specified, so every camera implemented its own configuration protocol, requiring individual tweaks on host side to fully support the camera. Fast forward to today and machine vision communications between the camera and host computer has been largely standardized, primarily using CoaXPress, GigE and USB interfaces. The new vision standards are more complex and require tighter timing margins than earlier generations. Further complications are provided by the fact that the standards themselves are evolving, requiring review of the standard and sometimes an upgrade of the transport layer implementation. The emergence of machine vision transport layer IP cores reduces the time required to develop camera-host interfaces. For example, Sensor to Image (S2I), a unit of Euresys, provides IP cores that meet the latest CXP, GigE Vision and USB3 Vision interface standards. These IP cores secure the interoperability of the camera and host while ensuring compliance with the latest version of the interface layer. S2I’s Vision Standard IP Cores solutions are delivered as a working reference design along with FPGA IP cores that have been fully tested against a wide range of popular frame grabbers and image acquisition libraries. The IP cores are compact, leaving plenty of room for additional vision functionality. They are compatible with Xilinx 7 and newer and Intel/Altera Cyclone V and more recent devices. The top-level design, consisting of the interface between external hardware such as the image sensor and transport layer PHY, is delivered as VHDL source code that can be adapted to custom hardware beyond the leading FPGA platforms supported by IP cores. The Video Acquisition Module of the reference design simulates a camera with a test pattern generator. This module is delivered as VHDL source code which is replaced by a sensor interface and pixel processing logic in the camera design. An FPGA integrated CPU (either MicroBlaze, NIOS or ARM) is used for several non-time-critical control and configuration tasks on the Vision Standard IP Cores. This software is written in C and can be extended by the customer. S2I has recently introduced an IMX Pregius IP core providing an interface to Sony Pregius Sub-LVDS image sensors. The company will also soon introduce an interface to MIPI sensors primarily used in embedded vision systems and mobile devices. The company offers a volume license best suited for companies with a large product line as well as a single-piece license which is the best option for companies with smaller lines.

Image 2 | MVDK evaluation board with MIPI CSI-2 sensor and CXP interface board. (Image: Euresys s.a.)

Happy Camera Suppliers

Ozray is a Korean machine vision camera supplier that has implemented IP cores in its area, line scan and thermal cameras. Keith Ahn, Executive Director and CTO, said that in-house development of CXP and GigE transport layer interfaces would have been considerably more expensive than purchasing IP. “By purchasing IP cores, we can focus internal engineering resources on image processing and controlling sensor functions to a degree that wasn’t possible in the past when so many resources were devoted to the camera-host interface,” Crevis is a leading supplier of machine vision cameras and industrial controllers at Korea. Crevis CEO June Hwang said that in the past it took a considerable amount of engineering manpower to develop the internal transmission logic, device drivers and Tx/Rx library for transport layer interfaces for its area scan cameras. “Now we purchase IP cores for GigE, CXP and USB interfaces from S2I while our engineers focus on developing sensor interface and camera functionality. S2I provides the reference design, training and technical support. This approach makes it possible to develop a reliable standard transmission interface in a fraction of the time required in the past. By incorporating IP cores into an FPGA that replaces many other parts, we have also reduced the size and manufacturing cost of our cameras.” Sick’s Ranger 3 camera offers a greater number of 3D profiles per second in combination with a large height range and high image quality. “Previous generations of the Ranger 3 used a proprietary GigE interface in order to provide capabilities that could not be delivered by following the standard,” said Mattias Johannesson, Senior Expert, Software 3D Camera for Sick IVP. “When the standard grew to include the features we needed, we wanted to adopt it but didn’t want to divert the engineering resources that would have been required to do the job internally. S2I offered a proven standard IP Core together with new custom modules to cover the extensions of the standard. Our engineering team was able to focus on our imager and signal processor, making it possible to get the latest Ranger 3 version to market in considerably less time than would have been required if we had developed the interface in-house.”